# UNA HERRAMIENTA WEB PARA EL CALCULO Y SIMULACION DE ESTRUCTURAS CACHE

# A. RIVAS, I. GONZALEZ, F.J.GOMEZ Y J. GARRIDO

Departamento de Ingeniería Informática. Escuela Técnica Superior de Informática. Universidad Autónoma de Madrid. E28049-Madrid. España.

La herramienta presentada facilita la resolución de problemas sencillos relacionados con el tamaño en bits de los campos en la palabra de direccionamiento, así como con el tamaño de la propia estructura de la unidad de memoria cache. Además permite la simulación del modo de operación de una memoria cache con unas características previamente seleccionadas. El objetivo es ayudar al alumno en la compresión del funcionamiento de la memoria cache y disponer de una herramienta que facilita el calculo de los parámetros asociados a su estructura. La aplicación se ha desarrollado en Java para que sea accesible desde la página web de la asignatura Arquitectura e Ingeniería de Computadores impartida en la E.T.S de Informática de la UAM.

#### 1. Introducción

Con las continuas mejoras en la infraestructura para la comunicación en red y en la tecnología para el acceso a Internet, aparece un nuevo reto en el mundo de la enseñanza. Este reto permite ofrecer al alumno un conjunto de nuevas herramientas accesibles de forma continua desde la red. Estas herramientas deben servir como complemento adicional a la clásica lección magistral sirviendo de ayuda en la tarea docente. La existencia de estas aplicaciones, permite tener aulas virtuales de enseñanza abiertas 24 horas y accesibles desde los domicilios particulares de los alumnos, con la única condición de disponer de conexión a Internet.

Programas para simular el funcionamiento de microprocesadores y los sistemas de memoria asociados, están disponibles en Internet y se emplean normalmente como complemento a los libros mas utilizados en la enseñanza de las asignaturas relacionadas con la arquitectura de ordenadores [1], [2]. Estas herramientas deben descargarse desde la red para su utilización. La aplicación propuesta en este trabajo sigue otra filosofía de funcionamiento y complementa trabajos de simulación ya desarrollados [3], siendo la característica mas relevante su integración en paginas Web y su utilización interactiva.

# 2. Objetivos docentes

En cualquier temario de un curso de arquitectura de computadores, el estudio de las mejoras habidas en la interfaz procesador-memoria es parte relevante. El estudio del sistema de jerarquía de memoria y en este contexto la memoria cache con sus diferentes arquitecturas, es considerado como parte esencial del mismo. Debido a la existencia de un gran número de implementaciones de cache, resulta muy complejo el análisis de todas ellas en un curso que no

sea monográfico del tema. Afortunadamente, existen unos pocos criterios básicos de diseño cuyo conocimiento y comprensión deben ser el principal objetivo de aprendizaje para los estudiantes. Dichos criterios, les deben permitir clasificar y diferenciar entre las diversas arquitecturas posibles. En la tabla-1 se muestran estos elementos clave:

| Tamaño                    | Bits de datos, de direccionamiento o asociativos y bits de control |

|---------------------------|--------------------------------------------------------------------|

| Estructura                | Asociativa (CA), Correspondencia Directa (CD) y Asociativa         |

|                           | por conjuntos o vías (AV)                                          |

| Algoritmos de sustitución | Aleatorio, L.R.U., L.F.U., F.I.F.O., otros                         |

| Política de escritura     | Escritura directa y post-escritura                                 |

| Número y niveles          | Unificada o dedicada, en uno o dos niveles.                        |

**Tabla 1:** Criterios básicos de diseño de estructuras cache.

Utilizando los enunciados de los problemas propuestos en clase o simplemente suponiendo cualquier sistema posible de memoria, gracias a la herramienta que se propone, el alumno puede manejar, interaccionando con el ordenador, infinitas posibilidades que le ayudan a entender los conceptos implicados en las tres primeras líneas de la tabla anterior.

Respecto al tamaño de la cache es importante que los alumnos observen, diferencien y sepan cuantificar, los diferentes tipos de bits que se pueden encontrar en una estructura cache. Cuando se habla del tamaño de una cache, no sólo se debe tener en consideración los bits dedicados a almacenar los datos, no se deben olvidar de aquellos dedicados al direccionamiento, bits tecnológicamente diferentes y especialmente costosos de implementar. Al mismo tiempo la presencia o ausencia de otros bits de control, como los bits de modificación o suciedad, los bits de validez o los bits de estado de los protocolos MESI, le deben informar de las características de la estructura que está analizando.

Aunque en términos de rendimiento del sistema de memoria, el tiempo de acceso medio es el parámetro más utilizado, la estructura y organización de la cache es otro elemento a tener en consideración. Conocer la diferencia entre las tres estructuras mas habituales y calcular en cada caso los bits implicados en su direccionamiento son conceptos que deben ser manejados con soltura. El análisis comparativo de estas estructuras es una tarea desarrollada en la herramienta que se presenta.

Con respecto a tercer elemento clave a analizar, la simulación de la cache, el objetivo de esta herramienta, no esta en conocer el comportamiento del sistema para miles de accesos, tarea para la que se usan aplicaciones estadísticas y test [4,5], sino en facilitar los conceptos en el funcionamiento de la estructura. La aplicación, utilizando ejemplos de pocas referencias, calcula los porcentajes de aciertos y fallos, permite diferenciar entre los tres modelos de estructuras ya comentados y facilita la comprensión de los algoritmos de reemplazamiento mas habituales.

### 3. Breve descripción de la aplicación

La aplicación ha sido desarrollada como un *applet* Java para facilitar su integración en una página Web. La herramienta presenta dos partes distinguibles por su funcionalidad. Por un lado el cálculo de tamaños de estructuras cache en función de unos parámetros dados y por el otro la simulación del funcionamiento de la memoria cache para una estructura previamente

definida. La utilización de la calculadora es muy simple, a partir de unas entradas facilitadas por medio de un formulario, genera su resultado en una ventana en formato ASCII. El simulador necesita como entrada un fichero suministrado por el usuario, que contiene la secuencia de accesos, el sistema muestra el contenido de la memoria en la ventana de simulación. Como un *applet* no puede acceder a un fichero en la maquina cliente en la que se está ejecutando, es necesario un paso previo que envía el fichero de usuario a la maquina servidor. Una aplicación cliente-servidor adicional, mantiene la comunicación entre el servidor Web y el *applet* para conseguir el acceso a los datos del fichero de usuario.

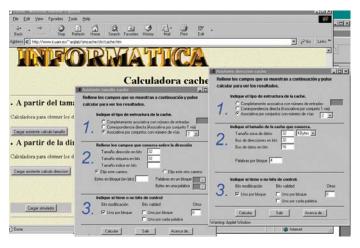

**Figura 1:** Página de Acceso a la aplicación y formularios de entrada para la calculadora cache

El *applet* integrado en la pagina web de la asignatura presenta el aspecto que se muestra en la figura 1.

La pagina de entrada, presenta tres posibles opciones de utilización:

La opción 1, denominada "Cálculo del tamaño de la cache", permite calcular el tamaño de la cache, a partir de la descripción de las características de la estructura de memoria. La segunda opción, llamada "Cálculo de dirección de cache". la complementa el caso anterior al calcular la estructura de la dirección cache utilizando la parámetro de entrada el tamaño total

de datos de la misma. La opción, "Simulación", visualiza el funcionamiento de una cache cuando se realiza una secuencia de accesos a memoria.

#### 4. Funcionamiento

Para utilizar la calculadora cache se selecciona una de las siguientes opciones dependiendo de los parámetros que sean conocidos en el problema propuesto.

- (a) CALCULO DE TAMAÑO: permite obtener el tamaño de la cache a partir de un sencillo formulario que se debe rellenar en tres pasos. En el primero se indica la organización de la estructura de la cache, CD, CA AV. En el segundo, se pide el tamaño del bus de direcciones, y la definición del tamaño de bloque en bytes. En el último paso se añade la información adicional relativa a los bits de control que se suponen para esta estructura cache. Una vez introducidos todos los datos, pulsando sobre el botón calcular, se presentan los resultados en una nueva ventana donde se resumen todos los datos relativos a la estructura cache. Estos datos, pueden imprimirse o ser guardados en un fichero de texto.

- (b) CALCULO DE CAMPOS EN LA DIRECCIÓN: análogamente al caso anterior, el cálculo del tamaño de los campos en los que se divide la dirección para el acceso a la cache, requiere rellenar un formulario dividido en tres etapas. La primera es idéntica al caso anterior, y en ella se indica el tipo de organización de la cache. En la siguiente se debe introducir el tamaño de la zona de datos de la cache y los tamaños de los buses de direcciones y de datos. Finalmente, se debe indicar las palabras por bloque. En la ultima etapa, se pueden indicar los

bits de control que se utilizan en la estructura cache. La presentación de los resultados del calculo es idéntica al caso anterior.

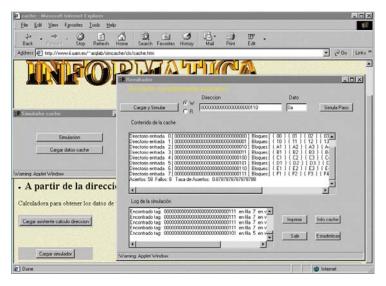

Por otro lado, se dispone de un simulador de funcionamiento de la estructura cache. Como paso previo, se debe elegir uno de los modelos predefinidos. En el ejemplo de la figura 2 se muestra el resultado obtenido para una pequeña cache CA con direcciones de acceso de 32 bits y 8 bloques con 8 bytes cada uno. Se utiliza un algoritmo LRU como política de reemplazo.

Figura 2: Simulador

Existen dos maneras de introducir datos en la cache. La primera, dato a dato, definiendo la dirección y el valor en hexadecimal. La segunda posibilidad, utiliza como entrada para el simulador, un fichero escrito en ASCII por el usuario. Este fichero contiene la secuencia de accesos a la memoria con un formato prefijado.

Otra opción, permite conocer, en cualquier momento de la simulación, las estadísticas de aciertos y fallos para los accesos realizados hasta el momento.

### 5. Conclusiones

Se presenta una herramienta web de fácil manejo y compresión que facilita la resolución de problemas referentes al tamaño y modo de direccionamiento de las posibles estructuras de una unidad cache. Utilizando pequeñas unidades caches unificadas con diferentes estructuras, la herramienta permite la simulación de sencillos programas escritos en lenguaje máquina, visualizando el contenido final de la memoria así como las tasas de fallos y aciertos que se han producido. La herramienta es un complemento ideal como apoyo docente en asignaturas relacionadas con arquitectura de computadores.

## Referencias

- [1] David A. Patterson y John L. Hennessy . *Estructuctura y diseño de computadores*. Vols. 1, 2 y 3. Ed. Reverte 2000.

- [2] W. Stalling. Organización y Arquitectura de Computadores. 5ª Edición. Prentice Hall 2000

- [3] J. García Zubia y S. Romero Yesa, Autor. *Simuladores de Computadores Básicos en Internet*. Vol I, 47-50, Actas del IV Congreso de TAEE2000. Barcelona.

- [4] <a href="http://www.cs.wisc.edu/~markhill/DineroIV/">http://www.cs.wisc.edu/~markhill/DineroIV/</a>

- [5] http://www-wjp.cs.uni-sb.de/~kroening/cache/cache-o-mat.html